Quantum computer with swappable logical qubits

US20240169240

2024-05-23

Physics

G06N10/40

Inventor:

Assignee:

Applicant:

Drawings (4 of 107)

Smart overview of the Invention

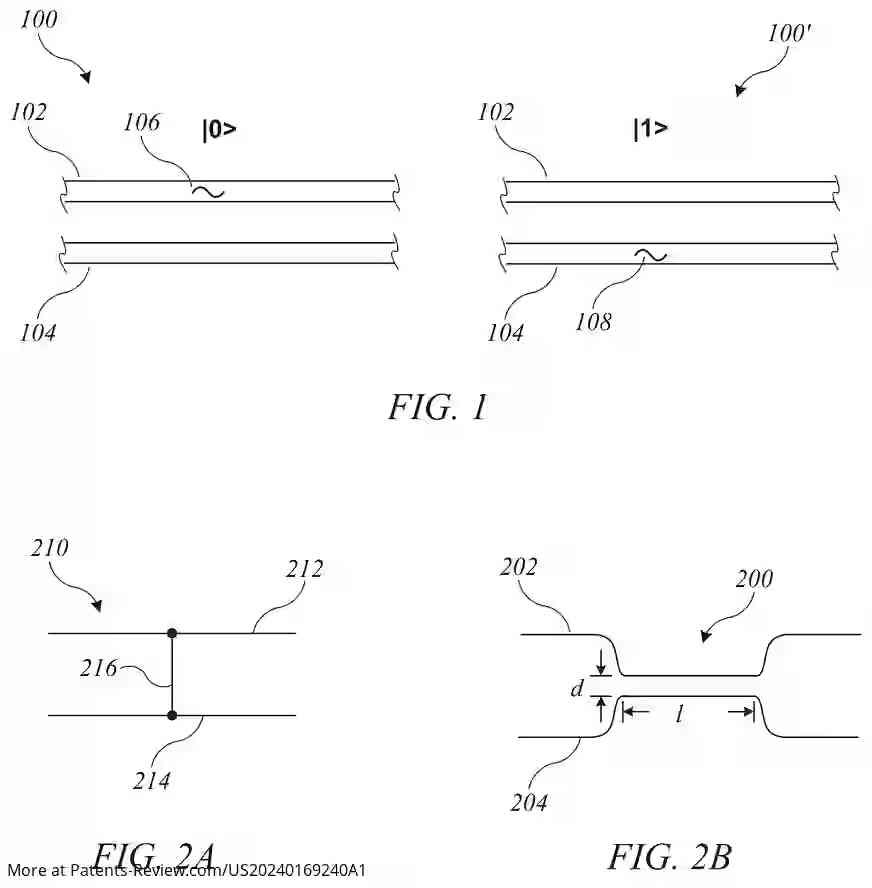

The patent application describes a fault-tolerant quantum computer architecture that utilizes topological codes, such as surface codes, to minimize idle volume. The system is composed of qubit modules that generate surface code patches for logical qubits, interconnected through a network allowing dynamic coupling and state transfer. This network features "port" connections for coupling boundaries of surface code patches and "quickswap" connections for transferring states between qubit modules.

Qubit Modules and Connections

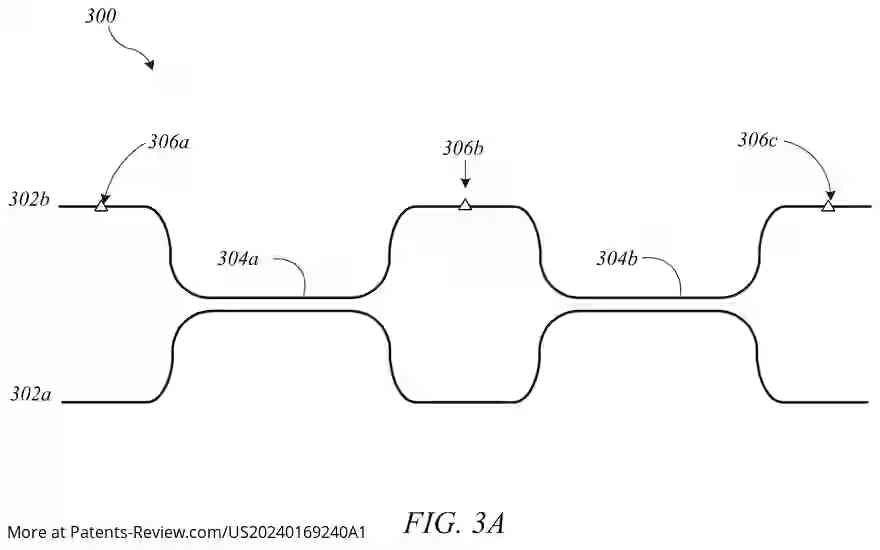

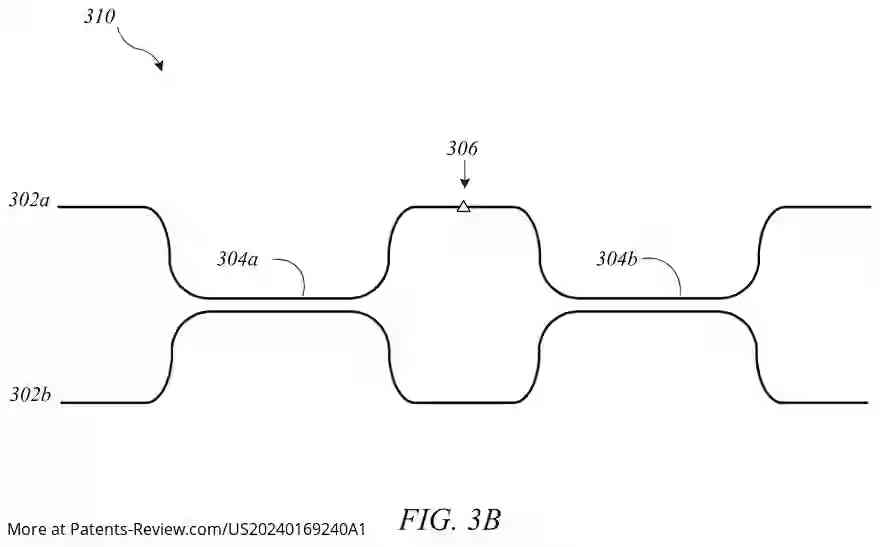

Qubit modules are central to the architecture, each equipped to handle physical qubits and generate topological code patches during multiple code cycles. The interconnections include port connections that enable selective coupling within a fixed range and quickswap connections forming a log-tree network. These quickswap connections allow state transfers between non-adjacent modules, enhancing flexibility and efficiency in quantum operations.

Quickswap Connections

Quickswap connections are designed to swap logical qubits between pairs of qubit modules within a single code cycle. They can connect each module to two or more others, facilitating concurrent swaps among disjoint module pairs. The system includes classical control logic circuitry to manage the operation of these quickswap connections, ensuring precise control over the quantum processes.

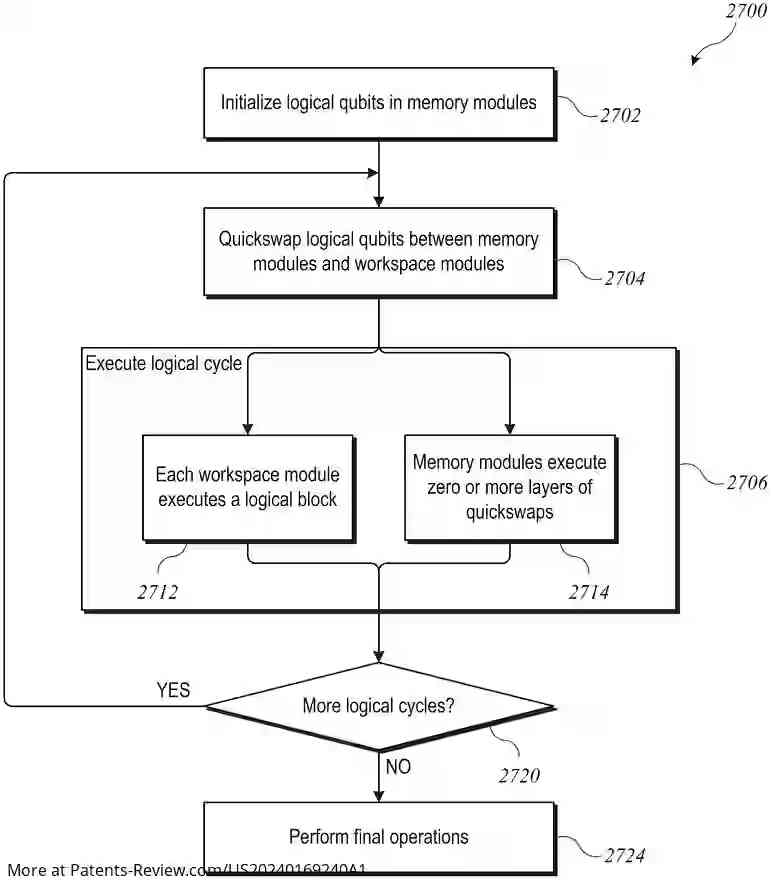

Methodology

The described method involves using workspace and memory qubit modules, where logical qubits are stored and swapped as needed. During logical cycles, quickswap operations move states between memory and workspace modules to execute logical gate operations across multiple code cycles. This dynamic rearrangement prepares the system for subsequent logical cycles, optimizing the execution of quantum computations.

Additional Features

The system can incorporate photonic qubits with optical waveguides for quickswap connections, enhancing communication speed and reliability. Port connections are also utilized for joint measurement operations between module pairs, further expanding the system's operational capabilities. This robust architecture aims to advance practical quantum computing by addressing key challenges in fault tolerance and scalability.