Complementary 2(N)-bit redundancy for single event upset prevention

US20240171179

2024-05-23

Electricity

H03K19/23

Inventor:

Assignee:

Applicant:

Drawings (4 of 9)

Smart overview of the Invention

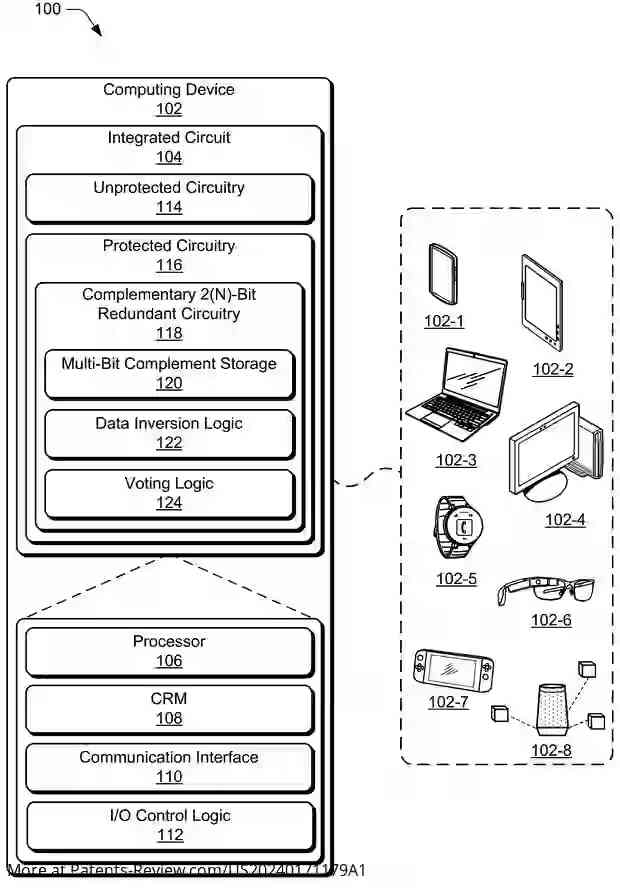

The disclosure introduces a method for enhancing the resilience of integrated circuits against single event upsets (SEUs) using complementary 2(N)-bit redundancy. This approach employs a combination of data storage elements and voting logic to store both data and its complement, enabling error detection and correction. The system dynamically adapts to different types of SEU failures, offering a robust mechanism to maintain data integrity in environments prone to radiation-induced errors.

Background

Integrated circuits are susceptible to SEUs, particularly in environments with high solar radiation. These upsets occur when charged particles alter a circuit's output by flipping bit values, potentially leading to malfunctions in critical devices like satellites and medical equipment. Traditional methods, such as triple modular redundancy, offer some protection but are vulnerable to deliberate attacks due to predictable element spacing.

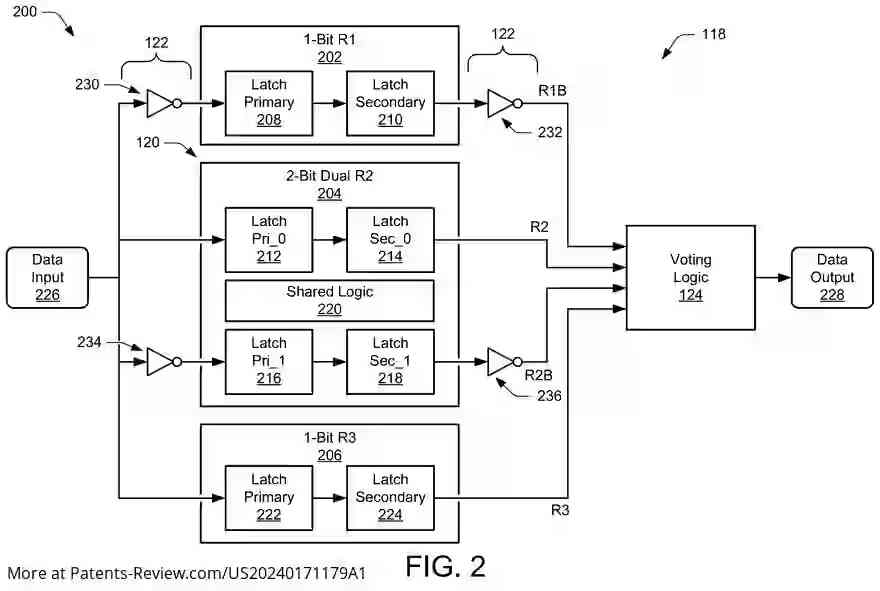

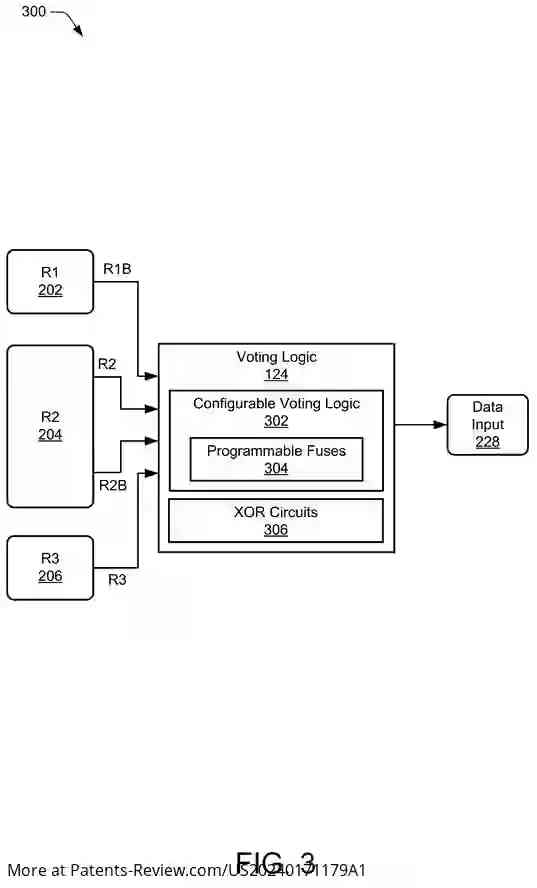

Complementary Redundancy

The proposed system incorporates complementary data storage within integrated circuits. It uses separate elements to store original and complementary data values, supported by voting logic that determines the correct output. This setup not only prevents SEUs by ensuring that both original and complementary values must be altered simultaneously for an error to propagate but also allows for dynamic error correction based on detected failures.

Implementation Details

The integrated circuit design includes an input node connected to both a data storage element and an inverter that provides the complementary value. A multi-bit storage element stores these values separately, while voting logic evaluates inputs from multiple storage elements to decide the final output. This approach ensures that at least three out of four logic values must be consistent for a valid output, significantly reducing the likelihood of SEU-induced errors.

Advantages and Applications

This redundancy technique offers enhanced protection against both accidental SEUs and deliberate attacks by diversifying stored states across different logic paths. The system's adaptability in configuring voting logic criteria allows it to address various failure modes effectively. This makes it suitable for mission-critical applications where reliability is paramount, such as aerospace, healthcare, and secure communications systems.