SUBTRACTIVELY PATTERNED INTERCONNECT STRUCTURES FOR INTEGRATED CIRCUITS

US20240304543

2024-09-12

Electricity

H01L23/5226

Inventors:

Assignee:

Applicant:

Drawings (4 of 56)

Smart overview of the Invention

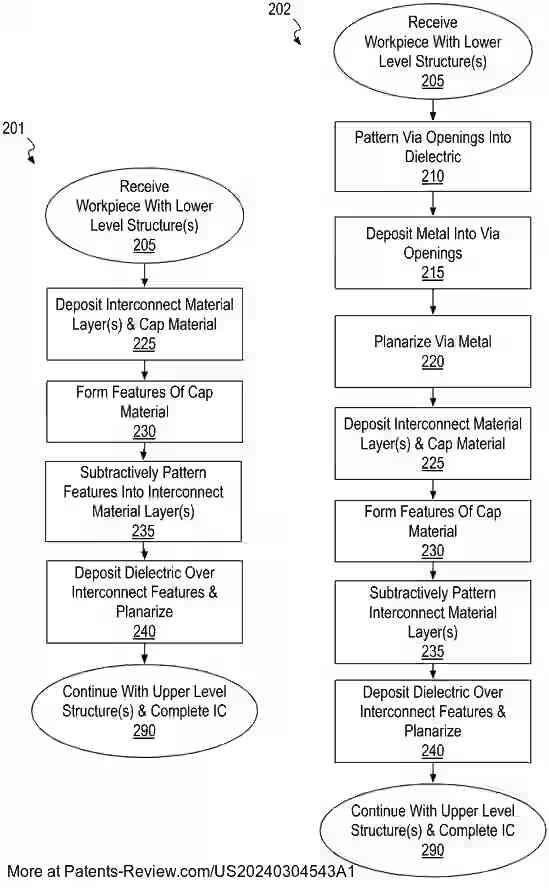

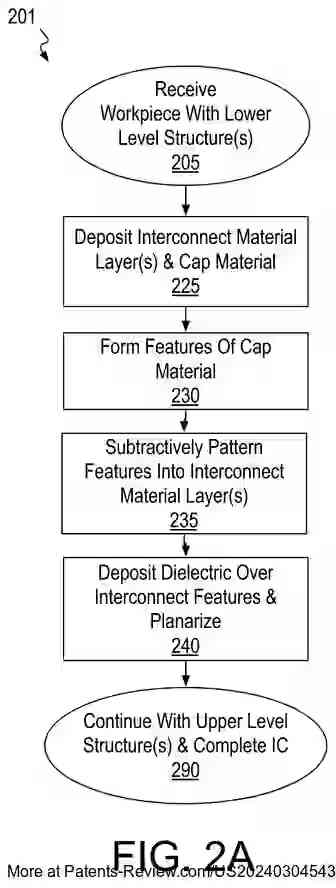

Integrated circuits (ICs) are increasingly becoming complex, necessitating the development of advanced interconnect structures. These structures utilize subtractively patterned features, which help in defining the ends of interconnect lines and vias with improved accuracy. By employing multiple patterning techniques and various cap materials, the potential for misregistration is significantly minimized, enhancing the overall performance of the IC.

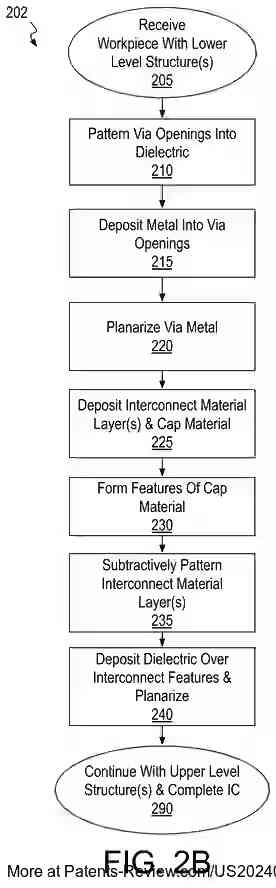

Integration of Features

The interconnect structures can integrate subtractively patterned features such as lines and vias in various configurations. These features may be combined with damascene techniques, where metals are deposited in a controlled manner to create connections between different interconnect levels. The innovative design allows for effective filling of vias and trenches, which is crucial for maintaining electrical connectivity in densely packed circuits.

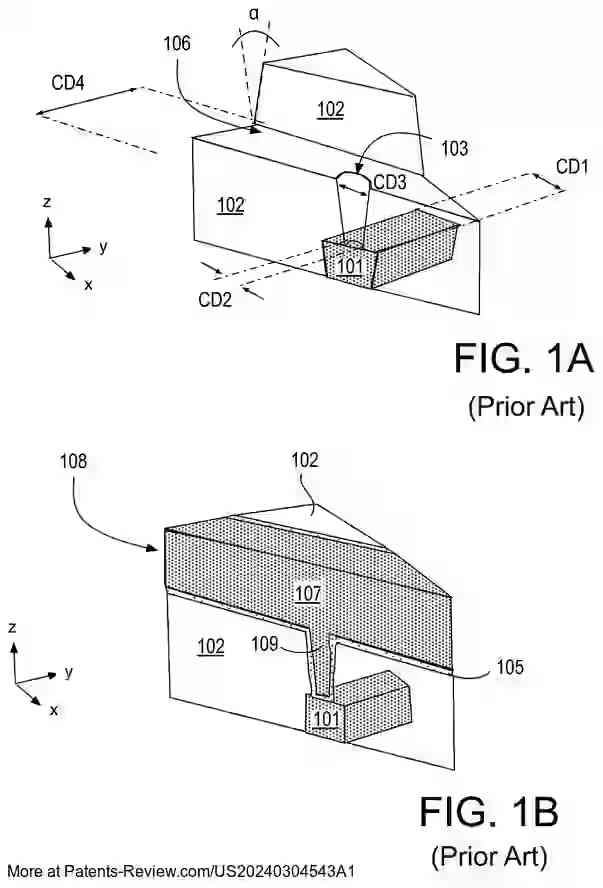

Challenges with Conventional Techniques

Traditional interconnect methods often face challenges due to increased resistance-capacitance (RC) delays as interconnect density rises. The use of diffusion barrier materials, while essential to prevent metal migration, can inadvertently increase electrical resistance. This is particularly problematic at critical junctions where minimal resistance is required for optimal circuit performance.

Barrier Material Innovations

New approaches involve the strategic placement of barrier materials within the subtractively patterned features. For instance, a bottom barrier can be selectively deposited to avoid unnecessary resistance at junctions where it is not needed. Materials such as graphene or specific metal chalcogenides may be employed to enhance performance while minimizing adverse effects on electrical conductivity.

Advantages of Multiple Patterning Techniques

The application of multiple patterning strategies allows for greater flexibility in defining interconnect features. By reducing misregistration between different subsets of features, these techniques enable more precise alignments within the IC architecture. This advancement not only improves the reliability of connections but also supports the ongoing trend towards higher performance and denser integrated circuits.